A VHDL program consists of a collection of **design units**, each of which is defined using three components

## **Library and Package Declaration**

```

library IEEE;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

```

Libraries and packages are collections of commonly used items, such as data types, subprograms and components

The above two packages define *std\_logic* and *std\_logic\_vector* data types, as well as *signed* and *unsigned*

I also find it extremely useful to create a file with my own data types and constants, that are then included declared below the *ieee* packages

```

library work;

use work.DataTypes_pkg.all;

```

# **Entity Declaration**

```

entity entity_name is

port (

port_names: mode data_type;

port_names: mode data_type;

port_names: mode data_type;

);

end entity_name;

```

port\_names are the **formal** signal names of the design unit, which are used to connect this design unit to pins on an FPGA or to other design units

The *mode* component can be **in**, **out** or **inout** (for bi-directional port)

ALWAYS use *std\_logic* and *std\_logic\_vector* as the data\_type in **entity** declarations

A common mistake with *mode* is to try to use a signal of mode **out** as an *input signal* within the architecture body

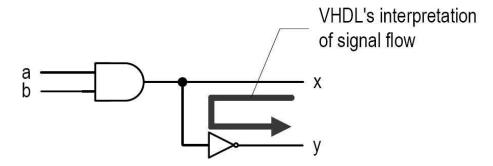

Consider:

```

library ieee;

use ieee.std_logic_1164.all;

entity mode_demo is

port (

a, b: in std_logic;

x, y: out std_logic);

end mode_demo;

architecture wrong arch of mode demo is

begin

x <= a not b;

y <= not x; -- ERROR!!!!

end wrong_arch;

```

Port signals defined to be *out* can NOT be read

This code reads and writes x so it must be defined as **inout** to avoid a syntax error But x is really not a bi-directional signal in the true sense of the word

The solution you will be forced to adopt is to create an *internal* signal as follows

```

architecture ok_arch of mode_demo is

signal ab: std_logic;

begin

ab <= a and b;

x \le ab;

y <= not ab;

end ok_arch;

```

# **Fundamental Elements of VHDL Architecture Body**

The architecture body specifies the logic functionality of the design unit

```

architecture arch_name of entity_name is

declarations

begin

concurrent_stmt;

concurrent_stmt;

end arch_name;

```

The declaration part is optional and can include internal signal declarations or constant declarations

There are several possibilities for *concurrent\_stmts*, which we will cover soon

Comments start with two dashes, e.g.,

-- This is a comment in VHDL

An **identifier** can only contain alphabetic letters, decimal digits and underscore; the first character *must be a letter* and the last character **cannot** be an underscore

VHDL is case **IN**sensitive, i.e., the following identifiers are the same nextstate, NextState, NEXTSTATE, nEXTsTATE

Smart convention: Use CAPITAL\_LETTERs for constant names and the suffix \_n to indicate active-low signals

Signal declaration

**signal** signal\_name, signal\_name, ... : data\_type

```

The std_logic_vector is an array of elements with std_logic data type

signal a: std logic vector(7 downto 0);

```

The **downto** syntax puts the most significant bit (7) on the left, which is the natural representation for numbers (I rarely use the (0 to n) syntax)

```

std_logic constants are enclosed in single quotes: '1' and '0'

std_logic_vector constants are enclosed in double quotes: "00101"

```

```

Signal assignment uses '<=', NOT '=' as in programming languages

signal name <= constant or signal name;

```

#### **Constant** declaration

```

constant const_name, ... : data_type := value_expr;

```

For example

```

constant BUS WIDTH LB: integer := 5;

constant BUS_WIDTH_NB: integer := 2**BUS_WIDTH_LB;

```

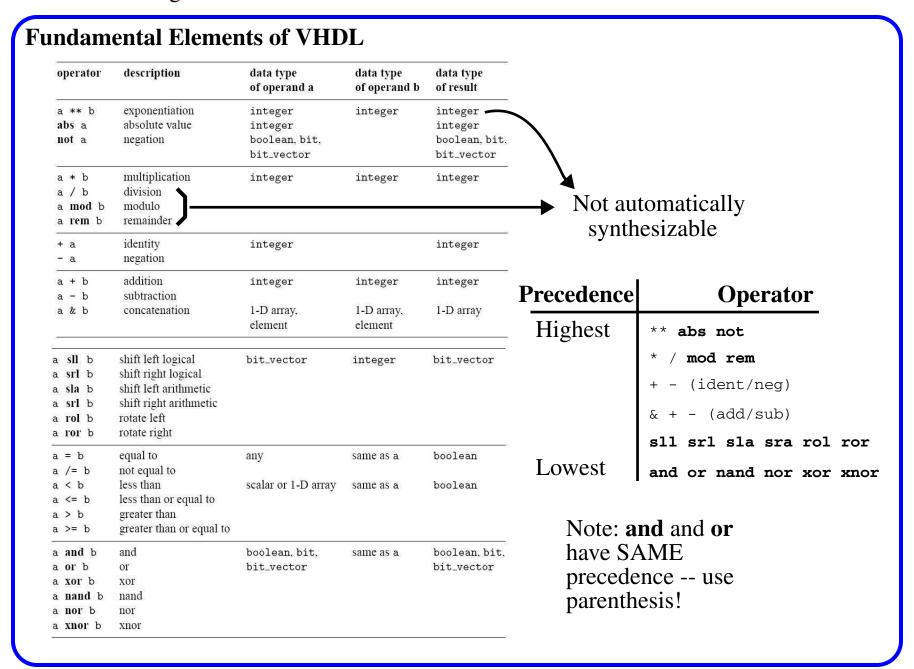

You will use *std\_logic\_vector* instead of *bit\_vector* as defined in the table

Division by powers of 2 can be used in signal assignment stmts, e.g., a/16 This is implemented by the synthesis tool as a right shift operation

Division by other numbers requires a design unit that implements the division!

VHDL is a strongly-typed language, requiring frequent type casting and conversion This is particularly evident with the *shift* operator

```

a <= resize(unsigned(b), 10) sll</pre>

to integer (unsigned(c));

```

Here, a is a unsigned of size 10 elements, and b and c are std\_logic\_vector

Bits or a range of bits can be referenced as

```

a(1)

a(7 downto 3)

```

VHDL relational operations, >, =, etc, must have operands of the same element type but their widths may differ

Avoid comparing operands of different widths, it's error prone

Concatenation operator (&) constructs and/or extends operands on the right Also used to force a match between width of the operands on left and right

```

y \le "00" \& a(7 downto 2);

y \le a(7) \& a(7) \& a(7 downto 2);

y \le a(1 \text{ downto } 0) \& a(7 \text{ downto } 2);

```

Also useful when defining a *shift register* as we will see later

### Array aggregate

```

a \ll (7|5=>'1', 6|4|3|2|1|0=>'0');

a <= (7 | 5=>'1', others=>'0');

a \le (7 \text{ downto } 3 = '0') \& b(7 \text{ downto } 5);

a <= (others=>'0');

```

Last assignment is very useful and works independent of the data type

## **IEEE numeric\_std package**

Standard VHDL and the *std\_logic\_1164* package support arithmetic operations only on *integer* data types

```

signal a, b, sum: integer;

sum <= a + b;

```

But this is inefficient in hardware because integer does NOT allow the range (number of bits) to be specified

We certainly don't want a 32-bit adder when an 8-bit adder would do

The *numeric\_std* package allows an array of 0's and 1's to be interpreted as an unsigned or signed number, using these names as the data type

```

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric std.all;

signal x, y: signed(15 downto 0);

```

For signed, the array is interpreted in 2's-complement format, with the MSB as the sign bit

Therefore "1100" represents 12 when interpreted as an unsigned number but -4 as a signed number

The *numeric\_std* package supports arithmetic operations, including those involving integer constants

```

signal a, b, c, d, e: unsigned(7 downto 0);

a <= b + c;

d \le b + 1;

e \le (5 + a + b) - c;

```

Note that the sum "wraps around" when overflow occurs, so BE VERY CAREFUL when choosing a size

| overloaded<br>operator                                 | description                | data type<br>of operand a                                  | data type<br>of operand b                                  | data type<br>of result                   |

|--------------------------------------------------------|----------------------------|------------------------------------------------------------|------------------------------------------------------------|------------------------------------------|

| abs a<br>– a                                           | absolute value<br>negation | signed                                                     | signed                                                     |                                          |

| a * b<br>a / b<br>a mod b<br>a rem b<br>a + b<br>a - b | arithmetic<br>operation    | unsigned<br>unsigned, natural<br>signed<br>signed, integer | unsigned, natural<br>unsigned<br>signed, integer<br>signed | unsigned<br>unsigned<br>signed<br>signed |

| a = b<br>a /= b<br>a < b<br>a <= b<br>a > b<br>a >= b  | relational<br>operation    | unsigned<br>unsigned, natural<br>signed<br>signed, integer | unsigned, natural<br>unsigned<br>signed, integer<br>signed | boolean<br>boolean<br>boolean            |

# $numeric\_std$ package definitions

| function                                                                       | description                                              | data type of operand a                                                 | data type of operand b | data type of<br>result        |

|--------------------------------------------------------------------------------|----------------------------------------------------------|------------------------------------------------------------------------|------------------------|-------------------------------|

| <pre>shift_left(a,b) shift_right(a,b) rotate_left(a,b) rotate_right(a,b)</pre> | shift left<br>shift right<br>rotate left<br>rotate right | unsigned, signed                                                       | natural                | same as a                     |

| resize(a,b) std_match(a,b)                                                     | resize array<br>compare '-'                              | unsigned, signed<br>unsigned, signed<br>std_logic_vector,<br>std_logic | natural<br>same as a   | same as a<br>boolean          |

| to_integer(a)<br>to_unsigned(a,b)<br>to_signed(a,b)                            | data type<br>conversion                                  | unsigned, signed natural integer                                       | natural<br>natural     | integer<br>unsigned<br>signed |

There are three *type conversion functions* in *numeric\_std* package

```

to_unsigned, to_signed and to_integer

```

Use to\_unsigned and to\_signed when assigning constants to unsigned and signed signals

a <= to\_unsigned(2048, 13);

Assumes a is unsigned and of width 13 a is assigned the constant 2048

a <= resize(unsigned(b), 10) s11</pre> to integer (unsigned(c));

Looked at this earlier -- sll operator requires an integer type as last operand a must be unsigned of width 10

a(to\_integer(b)) <= '1';

Indexing into *std\_logic\_vector* requires an integer data type Here b must be unsigned

Type casting is also possible between 'closely related' data types

| data type of a                            | to data type                  | conversion function / type casting                               |                 |

|-------------------------------------------|-------------------------------|------------------------------------------------------------------|-----------------|

| unsigned, signed signed, std_logic_vector | std_logic_vector<br>unsigned  | <pre>std_logic_vector(a) unsigned(a)</pre>                       | Type casting    |

| unsigned, signed natural integer          | integer<br>unsigned<br>signed | <pre>to_integer(a) to_unsigned(a, size) to_signed(a, size)</pre> | Type conversion |

```

signal u1, u2: unsigned(7 downto 0);

signal v1, v2, v3: std_logic_vector(7 downto 0);

signal sg: signed(7 downto 0);

u1 <= unsigned(v1);

v2 <= std_logic_vector(u2);</pre>

u2 <= unsigned(sq) + u1;

v3 <= std_logic_vector(unsigned(v1) + unsigned(v2));

```

Use *resize* to deal with width differences if they exist