#### **MOS: Metal-Oxide-Silicon**

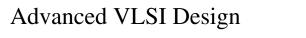

Metal gate has been replaced by **polysilicon** or **poly** in today's processes. Poly is used as a mask to allow precise definition of the source and drain regions.

Minimizes gate-to-source/drain overlap which is good for performance.

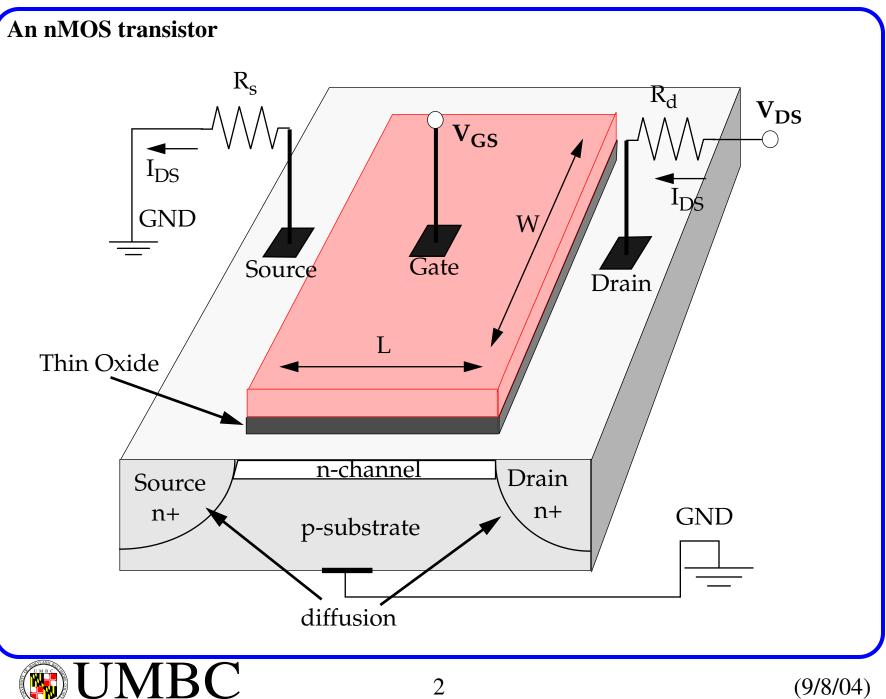

MOS structure created by superimposing several layers of conducting, insulating and transistor-forming materials.

Construction process is carried out on a *SINGLE* crystal of silicon. Wafers are 15-20 cm in diameter (6-8 inches).

CMOS: Two types of transistors are used, *pMOS* and *nMOS*.

*nMOS*: negatively doped silicon, rich in electrons. *pMOS*: positively doped silicon, rich in holes (the DUAL of electrons).

Advanced VLSI Design

| Advanced VLSI Design                                                                                                                                                   | Basics                                                                                | CMPE 640 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|----------|

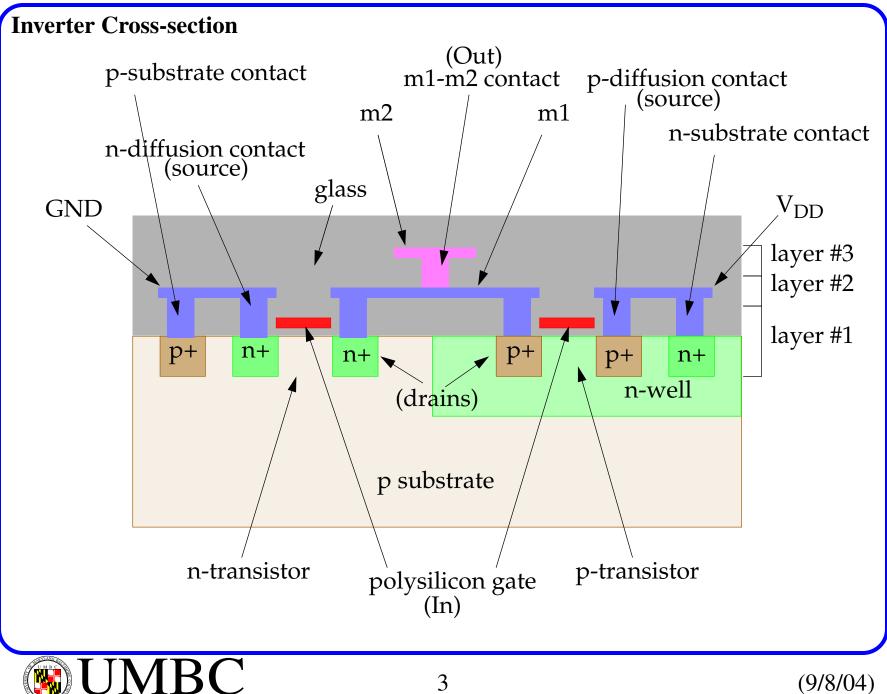

| MOS Transistors as Switches<br>We can treat MOS transistors as simple on-off switches with a source (S), gate<br>(G) (controls the state of the switch) and drain (D). |                                                                                       |          |

| Let '1' represent high vo<br>Let '0' represent low vol                                                                                                                 | ltage: typically V <sub>DD</sub> < 2.0 <sup>v</sup><br>tage: GND or V <sub>SS</sub> . | V.       |

- Signals such as '1' and '0' have **strength**, measures their ability to:

- Sink (to lower voltage, e.g. GND) or

- Source (from higher voltage, e.g. V<sub>DD</sub>) current.

*n*MOS and *p*MOS signal transmission strength:

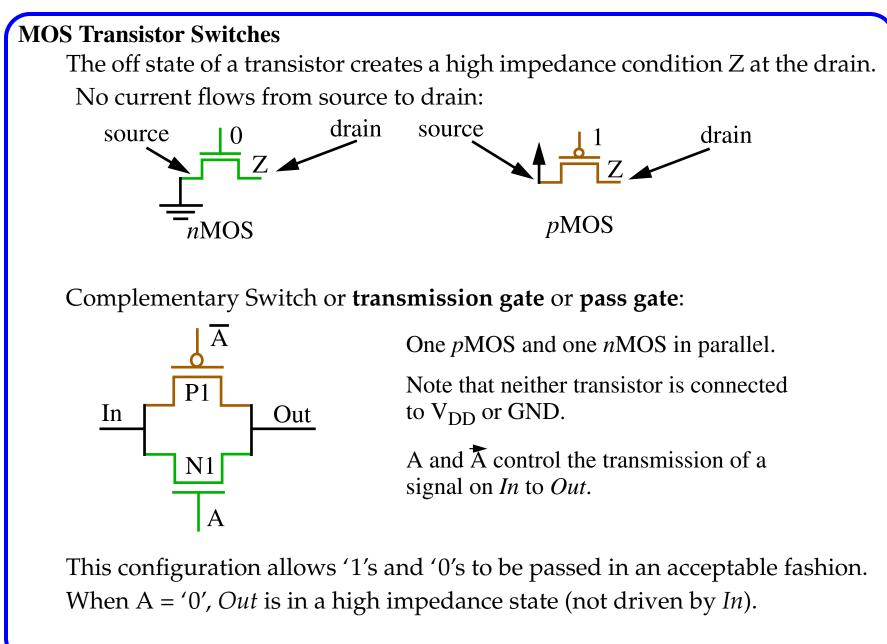

#### **MOS Transistor Switches**

The reason p-transistors are *poor* transmitters of logic 0 and n-transistors are *poor* transmitters of logic 1 is related to threshold voltage ( $V_t \sim = 500 \text{mV}$ ).

Threshold voltage will be discussed in detail soon.

Under the "switch" abstraction, G has complete control and S and D have no effect.

In reality, the gate can turn the switch on only if a *potential difference* of at least V<sub>t</sub> exists between the G and S.

This is clearly not the case for the "weak" bias configurations and "weak" 0s ( $\sim$ V<sub>t</sub>) and "weak" 1s ( $\sim$ V<sub>DD</sub>-V<sub>t</sub>) result.

Therefore, the following **buffer** implementation is a bad idea.

$$\begin{array}{c} A \\ \downarrow \\ P1 \\ \hline \\ Out \end{array} V_{DD} \\ BAD IDEA \\ \end{array}$$

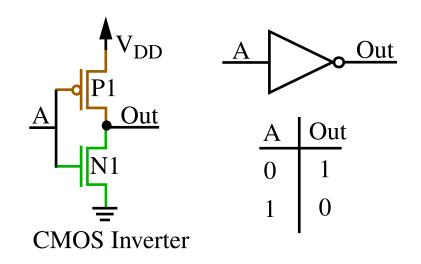

# The CMOS Inverter

If the gates of transistors P1 and N1 are not connected, then 4 possible output states are possible.

What are the two additional states?

Are any of these states undesirable?

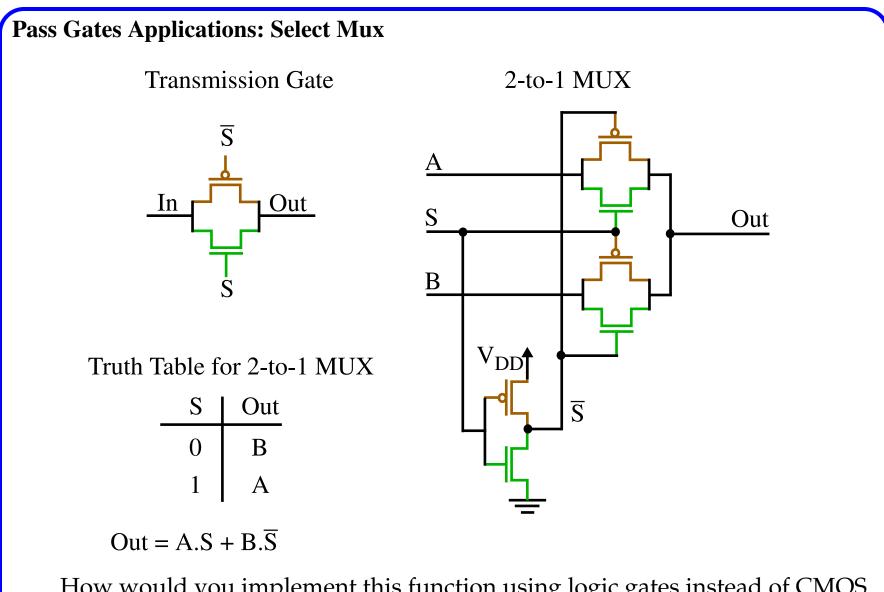

How would you implement this function using logic gates instead of CMOS switches?

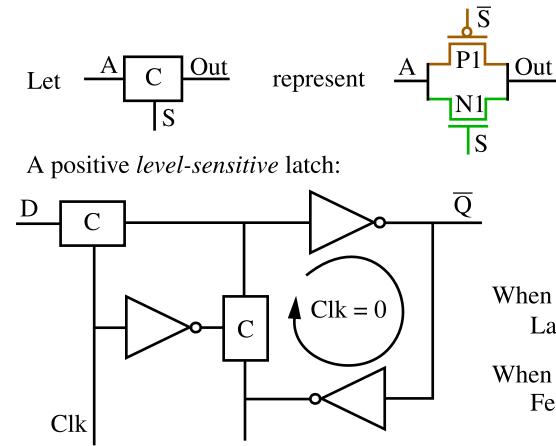

**Pass Gates Applications: Latches and Registers** The D latch:

State of the output is dependent on the level of the clock.

Although  $\overline{S}$  is not given in the "black box" abstraction, it must be routed to the pass gate.

The S "black box" terminal connects to the n-channel device.

When Clk = '1',  $\mathbf{Q}$  follows  $\mathbf{D}$ Latch is *transparent*

When Clk = '0', D is ignored, Feedback path is established.

Note: Other notations for  $\mathbf{D}$ : -D or DN or D.L.

# **Pass Gates Applications: Latches and Registers**

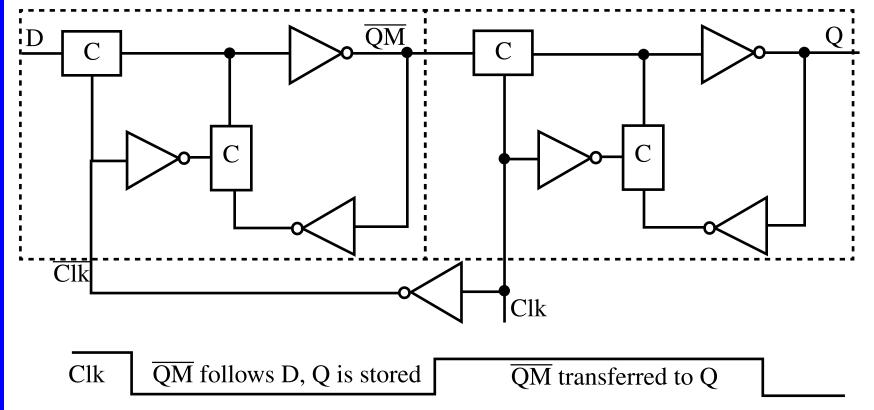

Master-Slave D Flip-Flop:

Combine one negative (master) and one positive (slave) *level-sensitive* latch.

Forms the basis of most CMOS storage elements (EXCEPTIONS: RAM and ROM).

We will look at memory elements in more detail later.

13

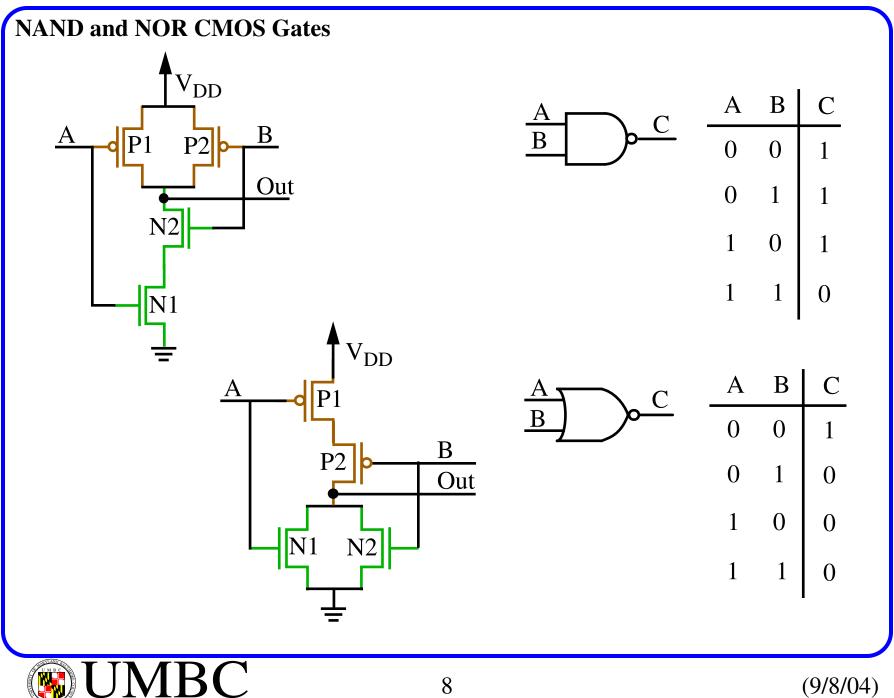

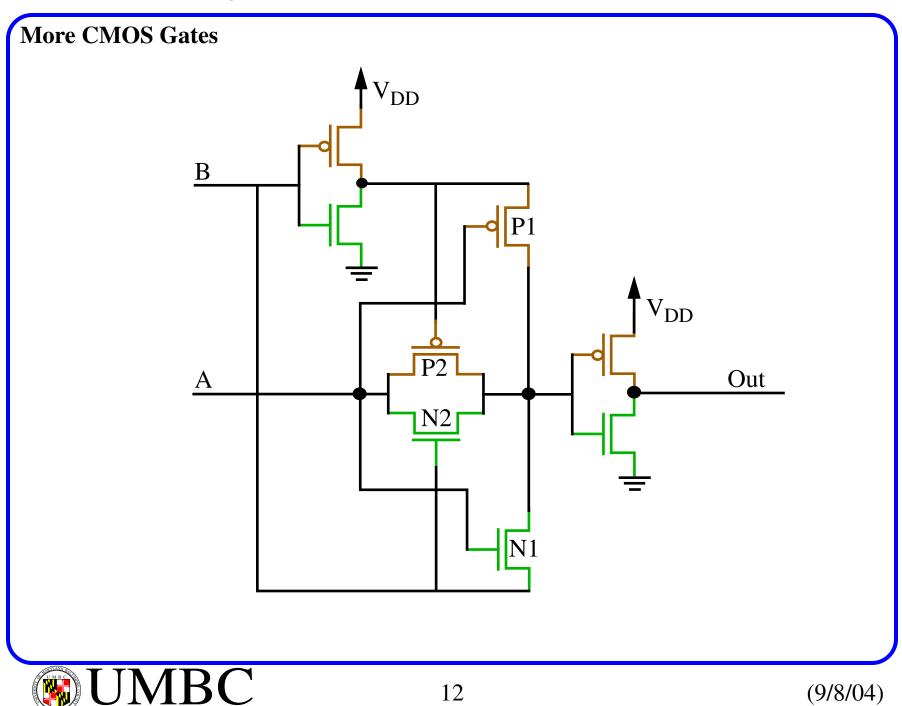

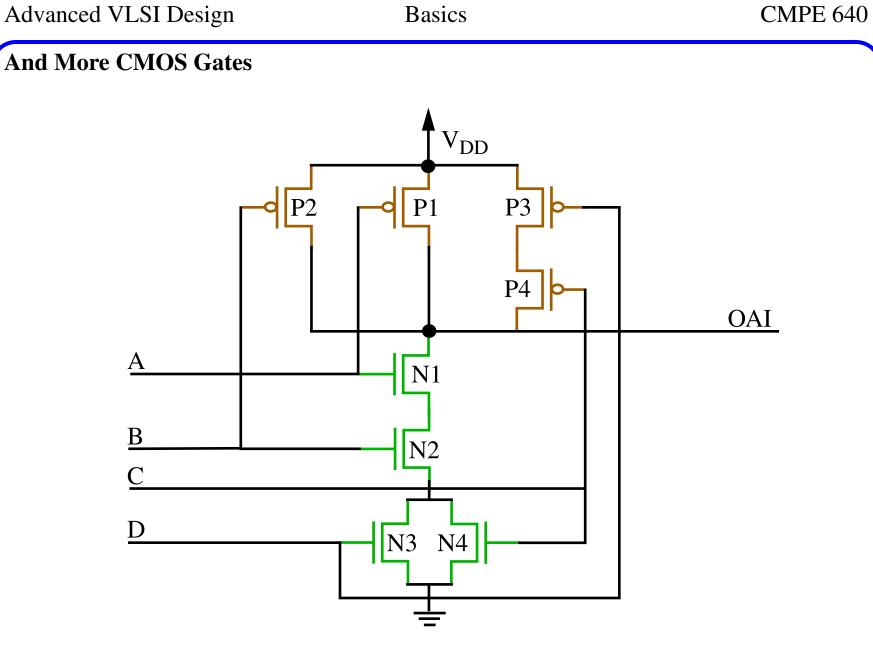

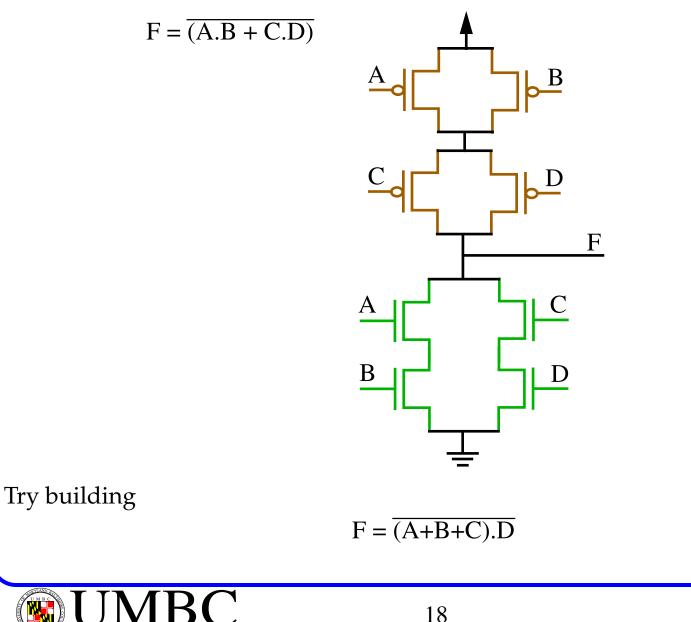

Building CMOS logic gates from expressions: How do we build ?  $F = \overline{(A.B + C.D)}$

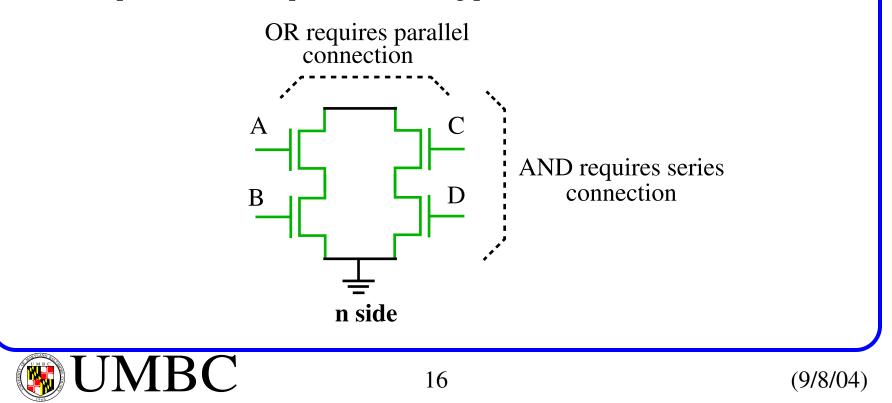

For the n-side, take the uninverted expression (the complement of F):  $\overline{F} = (A.B + C.D)$

AND expressions are implemented using series connections of n-transistors. OR expressions are implemented using parallel connections of n-transistors.

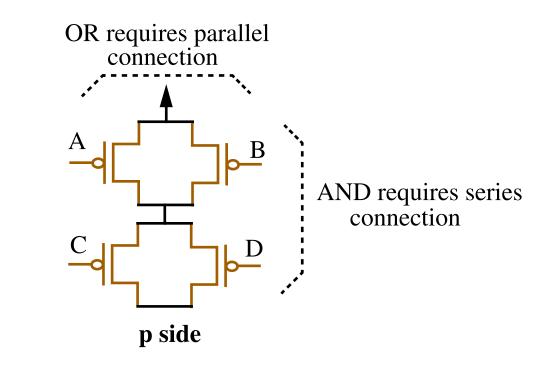

**Building CMOS logic gates from expressions:** For the p-side, invert expression used for n-expansion:  $((\overline{A}+\overline{B}).(\overline{C}+\overline{D}))$

AND expressions are implemented using series connections of p-transistors. OR expressions are implemented using parallel connections of p-transistors.

**Building CMOS logic gates from expressions:**

Combine to build function:

1) The previous analysis shows how to take a Boolean expression and create a transistor-level schematic diagram.

However, it assumes the Boolean expression is already in the appropriate form, which may not always be the case.

# **Boolean expression reduction:**

You should already know how to manipulate boolean expressions, e.g., using De Morgan's Laws, from exercises in other courses.

The objective is to reduce a boolean expression so that it can be realized in full-complementary CMOS using the minimum number of transistors.

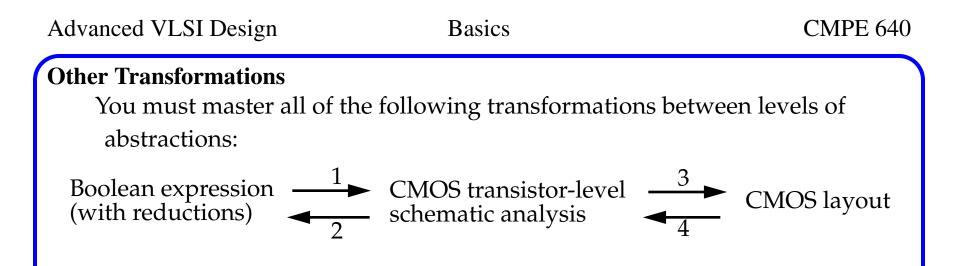

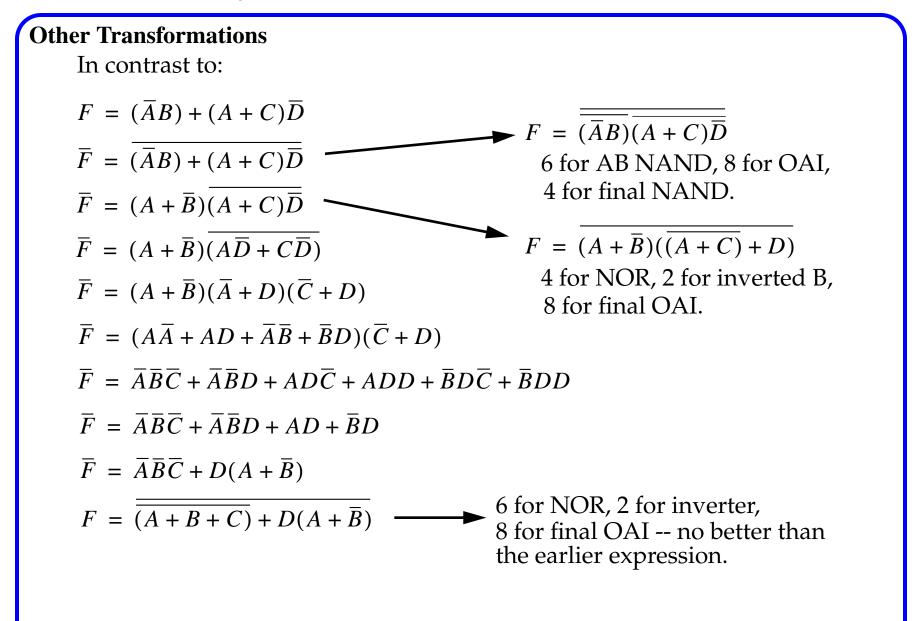

#### **Other Transformations**

In general, I am **not** expecting you to realize CMOS gates using *pass structures* in which the inputs are used to drive the output of the gate.

The XOR/XNOR implementations we saw earlier are examples of this.

The following heuristics can be applied as target reductions that will help you to obtain minimum realizations:

• Since CMOS is naturally inverting, you'll want to target a final expression of the form:

$F = \overline{(\text{expression})}$

• Many times only **un**complemented literals are available as signals in your circuit. Therefore, the reductions should attempt to **remove** the complemented literals in the Boolean expression.

Application of De Morgan's Laws can be used to transform complemented literals to NANDs and NORs.

• You should analyze each transformation to learn the trade-offs.

# **Other Transformations** For example: $F = (\overline{A}B) + (C+D)E$ Build inverse? 14 transistors The following reduction sequence can be applied that targets NANDs and removes the complemented literals: Invert both sides. $\overline{F} = (\overline{A}B) + (C+D)E$ $\overline{F} = \overline{\overline{A}B} \bullet \overline{(C+D)E}$ How many transistors are needed here? $\overline{F} = (A + \overline{B}) \bullet \overline{(C + D)E}$ Build here?: $F = (A + \overline{B}) \bullet \overline{(C + D)E}$ # transistors: 6 for OAI, 2 for inverter for B, 6 for final OAI. $\overline{F} = A\overline{(C+D)E} + \overline{B}\overline{(C+D)E}$ Multiply. $\overline{F} = A\overline{(C+D)E} + \overline{B+(C+D)E}$ $F = \overline{A(C+D)E} + \overline{B+(C+D)E}$ Or Build here?: 6 for OAI, 8 for B AOI, 6 for final AOL

# **Other Transformations**

Note that further reductions to NANDs and NORs may not pay off, as in the previous case.

In the next case, it is possible to get rid of an complemented literal without increasing the size of the OAI:

$$F = (\overline{A}B) + (C+D)\overline{E}$$

$$\overline{F} = \overline{(\overline{A}B)} + (C+D)\overline{E}$$

$$\overline{F} = \overline{\overline{A}B} \bullet \overline{(C+D)\overline{E}}$$

$$\overline{F} = (A+\overline{B}) \bullet \overline{(C+D)\overline{E}}$$

$\overline{F} = (A + \overline{B})(\overline{C + D} + E)$

Invert both sides.

Apply DeMorgan's Laws.

Build here?:

$F = (A + \overline{B}) \bullet \overline{(C + D)\overline{E}}$

# transistors: 6 for OAI, 4 for inverter for B, 6 for final OAI.

Or Build here?: 4 for NOR, 2 for inverter, 8 for final OAI.

Further transformations are not useful -- convince yourself.

# **Other Transformations** Expressions with repeated variables may be simplified to save a couple transistors, in some cases: $F = A\overline{BC} + \overline{A}CD$ $\overline{F} = A\overline{BC} + \overline{A}CD$ 4 + 2 + 10 + 2 $\overline{F} = (\overline{A} + BC)(A + \overline{CD})$ 2 + 4 + 10 $\overline{F} = \overline{A}A + \overline{A}\overline{CD} + ABC + BC\overline{CD}$ $BC\overline{CD}$ is redundant (covered) by the other terms, e.g, $\overline{F} = \overline{A}\overline{CD} + BC(A + \overline{CD}) = \overline{A}\overline{CD} + BC(A + \overline{A}\overline{CD})$ $\overline{F} = \overline{A}\overline{CD} + ABC$ 2 + 4 + 10 $\overline{F} = (\overline{A + CD}) + ABC$ 6 + 8 (\*14\*) $F = (\overline{A + CD}) + ABC$

#### **Other Transformations**

Sometimes it is best to implement the *inverse* function and add an inverter. For example, Carry, which has all uncomplemented inputs.

Carry =  $AB + C_{in}(A + B)$

$\overline{\text{Carry}} = \overline{AB + C_{in}(A + B)}$

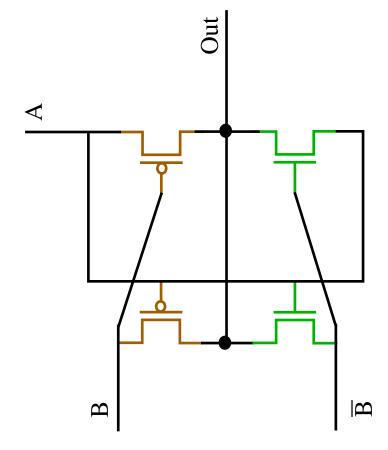

What about XOR and XNOR?

$$F = A\overline{B} + \overline{A}B$$

$$\overline{F} = \overline{A\overline{B} + \overline{A}B}$$

$$F = (\overline{\overline{A} + B})(A + \overline{B})$$

$$F = \overline{AB + \overline{A}\overline{B}}$$

$$F = \overline{AB + (\overline{A + B})}$$

How many transistors are needed here?

The best way to learn this is through practice.

Simply make up an expression of multiple variables and invert a couple of the literals and/or subexpressions.

#### **Other Transformations**

2) Translating from **transistor-level schematics** to **Boolean expressions** is straightforward.

Simply write the *n*-tree expression using the rules for series and parallel transistors given earlier.

Invert the final expression.

- 3) Translating from **transistor-level schematic** diagrams to **layout** is covered in the laboratories.

- 4) Translating from **layout** to **transistor-level schematic** diagrams is also covered in the laboratories.

- $\bullet$  In general, start by identifying the transistor sources connected to  $V_{\rm DD}$  or GND nodes.

- Add series transistors in the schematic for transistors whose sources are connected to drains of the previously identified transistors.

- Add parallel transistors at fan-out points.

- Label the transistors so it possible to connect the gates properly by tracing the poly connections.